+

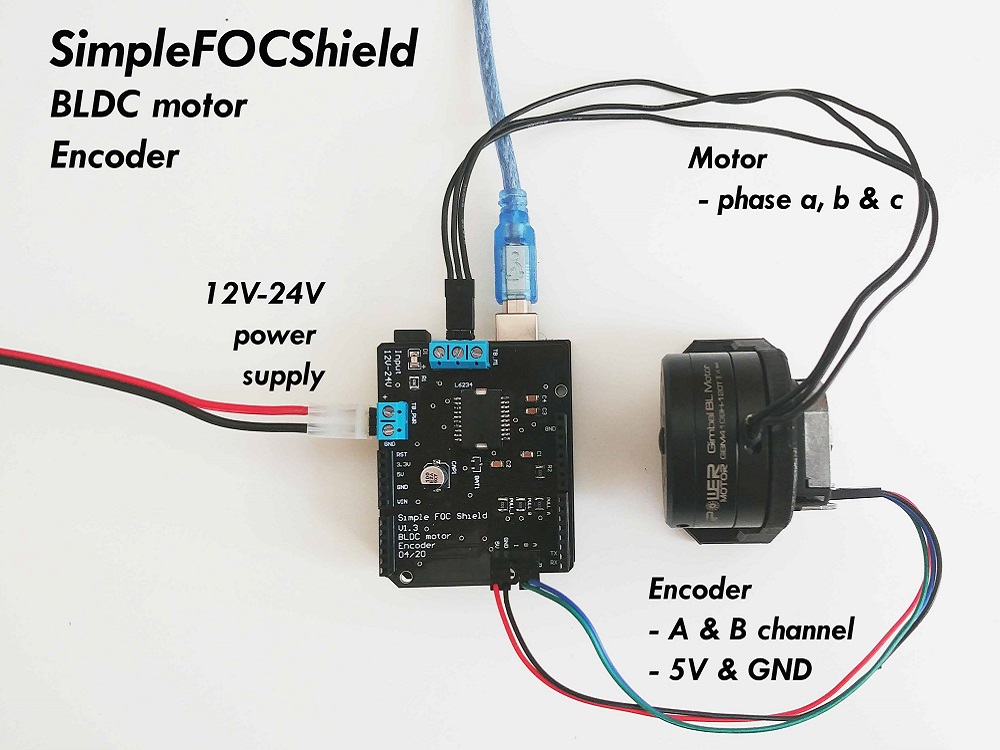

+// BLDCMotor( pole_pairs )

+BLDCMotor motor = BLDCMotor(11);

+// BLDCDriver( pin_pwmA, pin_pwmB, pin_pwmC, enable (optional) )

+BLDCDriver3PWM driver = BLDCDriver3PWM(9, 10, 11, 8);

+// Encoder(pin_A, pin_B, CPR)

+Encoder encoder = Encoder(2, 3, 2048);

+// channel A and B callbacks

+void doA(){encoder.handleA();}

+void doB(){encoder.handleB();}

+

+

+void setup() {

+ // initialize encoder hardware

+ encoder.init();

+ // hardware interrupt enable

+ encoder.enableInterrupts(doA, doB);

+ // link the motor to the sensor

+ motor.linkSensor(&encoder);

+

+ // power supply voltage [V]

+ driver.voltage_power_supply = 12;

+ // initialise driver hardware

+ driver.init();

+ // link driver

+ motor.linkDriver(&driver);

+

+ // set control loop type to be used

+ motor.controller = MotionControlType::velocity;

+ // initialize motor

+ motor.init();

+

+ // align encoder and start FOC

+ motor.initFOC();

+}

+

+void loop() {

+ // FOC algorithm function

+ motor.loopFOC();

+

+ // velocity control loop function

+ // setting the target velocity or 2rad/s

+ motor.move(2);

+}

+```

+You can find more details in the [SimpleFOC documentation](https://docs.simplefoc.com/).

+

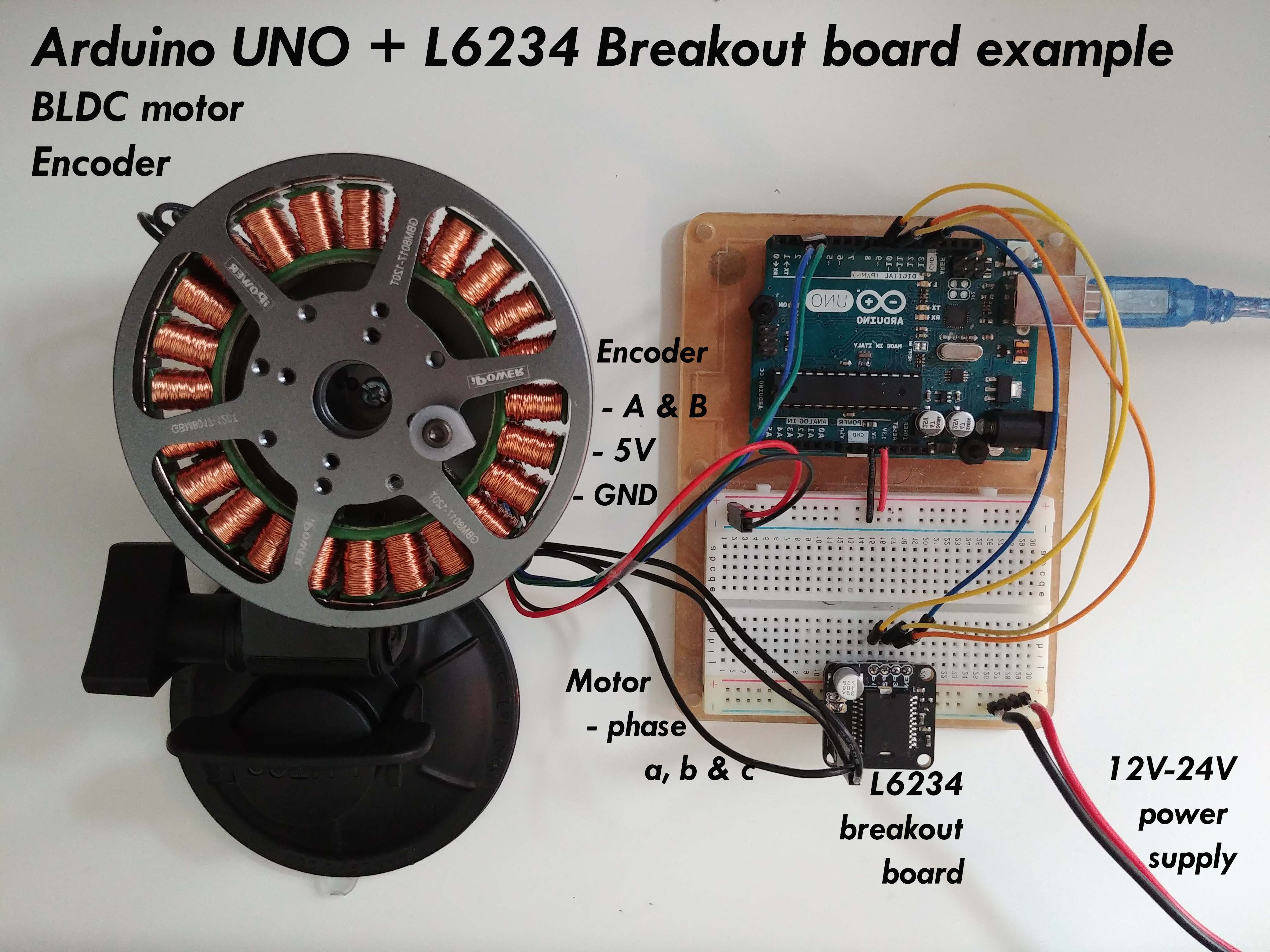

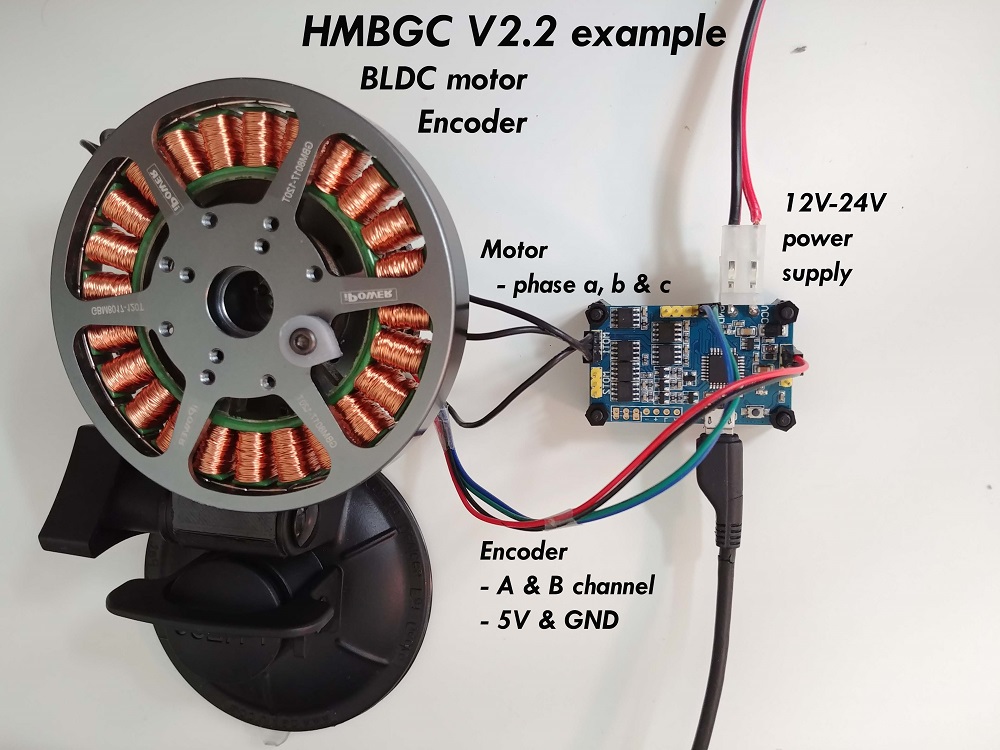

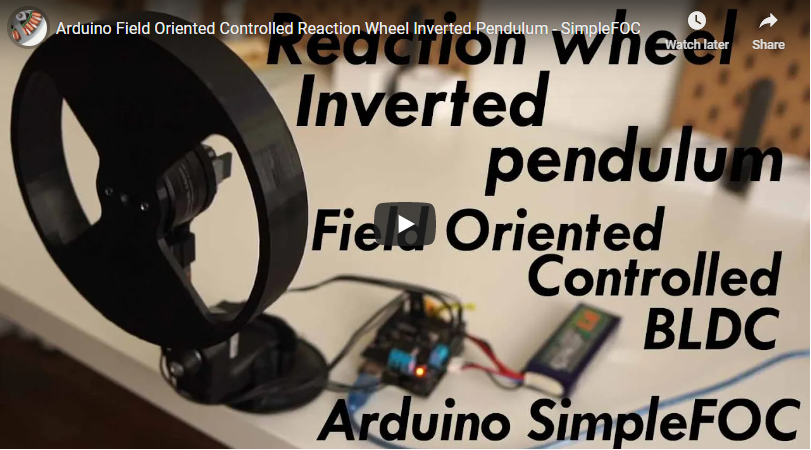

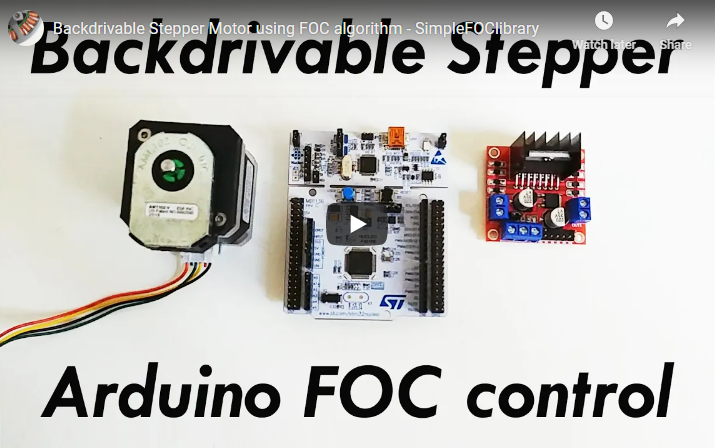

+## Example projects

+Here are some of the *Simple**FOC**library* and *Simple**FOC**Shield* application examples.

+

+

+ +

+

+

+

+

+ +

+

+

+

+

+ +

+

+

+

+

+ +

+

+

+

+

+

+## Citing the *SimpleFOC*

+

+We are very happy that *Simple**FOC**library* has been used as a component of several research project and has made its way to several scientific papers. We are hoping that this trend is going to continue as the project matures and becomes more robust!

+A short resume paper about *Simple**FOC*** has been published in the Journal of Open Source Software:

+

+ SimpleFOC: A Field Oriented Control (FOC) Library for Controlling Brushless Direct Current (BLDC) and Stepper Motors.

+ A. Skuric, HS. Bank, R. Unger, O. Williams, D. González-Reyes

+Journal of Open Source Software, 7(74), 4232, https://doi.org/10.21105/joss.04232

+

+

+If you are interested in citing *Simple**FOC**library* or some other component of *Simple**FOC**project* in your research, we suggest you to cite our paper:

+

+```bib

+@article{simplefoc2022,

+ doi = {10.21105/joss.04232},

+ url = {https://doi.org/10.21105/joss.04232},

+ year = {2022},

+ publisher = {The Open Journal},

+ volume = {7},

+ number = {74},

+ pages = {4232},

+ author = {Antun Skuric and Hasan Sinan Bank and Richard Unger and Owen Williams and David González-Reyes},

+ title = {SimpleFOC: A Field Oriented Control (FOC) Library for Controlling Brushless Direct Current (BLDC) and Stepper Motors},

+ journal = {Journal of Open Source Software}

+}

+

+```

diff --git a/embedded/CANFDMigrate/.pio/libdeps/seeed_xiao_esp32s3/Simple FOC/examples/hardware_specific_examples/B_G431B_ESC1/B_G431B_ESC1.ino b/embedded/CANFDMigrate/.pio/libdeps/seeed_xiao_esp32s3/Simple FOC/examples/hardware_specific_examples/B_G431B_ESC1/B_G431B_ESC1.ino

new file mode 100644

index 0000000..f1eeefd

--- /dev/null

+++ b/embedded/CANFDMigrate/.pio/libdeps/seeed_xiao_esp32s3/Simple FOC/examples/hardware_specific_examples/B_G431B_ESC1/B_G431B_ESC1.ino

@@ -0,0 +1,114 @@

+/**

+ * B-G431B-ESC1 position motion control example with encoder

+ *

+ */

+#include

+

+// Motor instance

+BLDCMotor motor = BLDCMotor(11);

+BLDCDriver6PWM driver = BLDCDriver6PWM(A_PHASE_UH, A_PHASE_UL, A_PHASE_VH, A_PHASE_VL, A_PHASE_WH, A_PHASE_WL);

+// Gain calculation shown at https://community.simplefoc.com/t/b-g431b-esc1-current-control/521/21

+LowsideCurrentSense currentSense = LowsideCurrentSense(0.003f, -64.0f/7.0f, A_OP1_OUT, A_OP2_OUT, A_OP3_OUT);

+

+

+// encoder instance

+Encoder encoder = Encoder(A_HALL2, A_HALL3, 2048, A_HALL1);

+

+// Interrupt routine intialisation

+// channel A and B callbacks

+void doA(){encoder.handleA();}

+void doB(){encoder.handleB();}

+void doIndex(){encoder.handleIndex();}

+

+// instantiate the commander

+Commander command = Commander(Serial);

+void doTarget(char* cmd) { command.motion(&motor, cmd); }

+

+void setup() {

+

+ // use monitoring with serial

+ Serial.begin(115200);

+ // enable more verbose output for debugging

+ // comment out if not needed

+ SimpleFOCDebug::enable(&Serial);

+

+ // initialize encoder sensor hardware

+ encoder.init();

+ encoder.enableInterrupts(doA, doB);

+

+ // link the motor to the sensor

+ motor.linkSensor(&encoder);

+

+ // driver config

+ // power supply voltage [V]

+ driver.voltage_power_supply = 12;

+ driver.init();

+ // link the motor and the driver

+ motor.linkDriver(&driver);

+ // link current sense and the driver

+ currentSense.linkDriver(&driver);

+

+ // current sensing

+ currentSense.init();

+ // no need for aligning

+ currentSense.skip_align = true;

+ motor.linkCurrentSense(¤tSense);

+

+ // aligning voltage [V]

+ motor.voltage_sensor_align = 3;

+ // index search velocity [rad/s]

+ motor.velocity_index_search = 3;

+

+ // set motion control loop to be used

+ motor.controller = MotionControlType::velocity;

+

+ // contoller configuration

+ // default parameters in defaults.h

+

+ // velocity PI controller parameters

+ motor.PID_velocity.P = 0.2;

+ motor.PID_velocity.I = 20;

+ // default voltage_power_supply

+ motor.voltage_limit = 6;

+ // jerk control using voltage voltage ramp

+ // default value is 300 volts per sec ~ 0.3V per millisecond

+ motor.PID_velocity.output_ramp = 1000;

+

+ // velocity low pass filtering time constant

+ motor.LPF_velocity.Tf = 0.01;

+

+ // angle P controller

+ motor.P_angle.P = 20;

+ // maximal velocity of the position control

+ motor.velocity_limit = 4;

+

+ // comment out if not needed

+ motor.useMonitoring(Serial);

+

+ // initialize motor

+ motor.init();

+ // align encoder and start FOC

+ motor.initFOC();

+

+ // add target command T

+ command.add('T', doTarget, "target angle");

+

+ Serial.println(F("Motor ready."));

+ Serial.println(F("Set the target angle using serial terminal:"));

+ _delay(1000);

+}

+

+void loop() {

+ // main FOC algorithm function

+ motor.loopFOC();

+

+ // Motion control function

+ motor.move();

+

+ // function intended to be used with serial plotter to monitor motor variables

+ // significantly slowing the execution down!!!!

+ // motor.monitor();

+

+ // user communication

+ command.run();

+}

diff --git a/embedded/CANFDMigrate/.pio/libdeps/seeed_xiao_esp32s3/Simple FOC/examples/hardware_specific_examples/B_G431B_ESC1/build_opt.h b/embedded/CANFDMigrate/.pio/libdeps/seeed_xiao_esp32s3/Simple FOC/examples/hardware_specific_examples/B_G431B_ESC1/build_opt.h

new file mode 100644

index 0000000..6f547ec

--- /dev/null

+++ b/embedded/CANFDMigrate/.pio/libdeps/seeed_xiao_esp32s3/Simple FOC/examples/hardware_specific_examples/B_G431B_ESC1/build_opt.h

@@ -0,0 +1 @@

+-DHAL_OPAMP_MODULE_ENABLED

\ No newline at end of file

diff --git a/embedded/CANFDMigrate/.pio/libdeps/seeed_xiao_esp32s3/Simple FOC/examples/hardware_specific_examples/Bluepill_examples/encoder/bluepill_position_control/bluepill_position_control.ino b/embedded/CANFDMigrate/.pio/libdeps/seeed_xiao_esp32s3/Simple FOC/examples/hardware_specific_examples/Bluepill_examples/encoder/bluepill_position_control/bluepill_position_control.ino

new file mode 100644

index 0000000..b29e45d

--- /dev/null

+++ b/embedded/CANFDMigrate/.pio/libdeps/seeed_xiao_esp32s3/Simple FOC/examples/hardware_specific_examples/Bluepill_examples/encoder/bluepill_position_control/bluepill_position_control.ino

@@ -0,0 +1,119 @@

+/**

+ *

+ * STM32 Bluepill position motion control example with encoder

+ *

+ * The same example can be ran with any STM32 board - just make sure that put right pin numbers.

+ *

+ */

+#include

+

+// Motor instance

+BLDCMotor motor = BLDCMotor(11);

+// BLDCDriver3PWM(IN1, IN2, IN3, enable(optional))

+BLDCDriver3PWM driver = BLDCDriver3PWM(PB6, PB7, PB8, PB5);

+// BLDCDriver6PWM(IN1_H, IN1_L, IN2_H, IN2_L, IN3_H, IN3_L, enable(optional))

+//BLDCDriver6PWM driver = BLDCDriver6PWM(PA8, PB13, PA9, PB14, PA10, PB15, PB12);

+

+// encoder instance

+Encoder encoder = Encoder(PA8, PA9, 8192, PA10);

+

+// Interrupt routine intialisation

+// channel A and B callbacks

+void doA(){encoder.handleA();}

+void doB(){encoder.handleB();}

+void doI(){encoder.handleIndex();}

+

+

+// angle set point variable

+float target_angle = 0;

+// instantiate the commander

+Commander command = Commander(Serial);

+void doTarget(char* cmd) { command.scalar(&target_angle, cmd); }

+

+

+void setup() {

+

+ // use monitoring with serial

+ Serial.begin(115200);

+ // enable more verbose output for debugging

+ // comment out if not needed

+ SimpleFOCDebug::enable(&Serial);

+

+ // initialize encoder sensor hardware

+ encoder.init();

+ encoder.enableInterrupts(doA, doB, doI);

+ // link the motor to the sensor

+ motor.linkSensor(&encoder);

+

+ // driver config

+ // power supply voltage [V]

+ driver.voltage_power_supply = 12;

+ driver.init();

+ // link the motor and the driver

+ motor.linkDriver(&driver);

+

+ // aligning voltage [V]

+ motor.voltage_sensor_align = 3;

+ // index search velocity [rad/s]

+ motor.velocity_index_search = 3;

+

+ // set motion control loop to be used

+ motor.controller = MotionControlType::velocity;

+

+ // contoller configuration

+ // default parameters in defaults.h

+

+ // velocity PI controller parameters

+ motor.PID_velocity.P = 0.2f;

+ motor.PID_velocity.I = 20;

+ // default voltage_power_supply

+ motor.voltage_limit = 6;

+ // jerk control using voltage voltage ramp

+ // default value is 300 volts per sec ~ 0.3V per millisecond

+ motor.PID_velocity.output_ramp = 1000;

+

+ // velocity low pass filtering time constant

+ motor.LPF_velocity.Tf = 0.01f;

+

+ // angle P controller

+ motor.P_angle.P = 20;

+ // maximal velocity of the position control

+ motor.velocity_limit = 4;

+

+

+ // comment out if not needed

+ motor.useMonitoring(Serial);

+

+ // initialize motor

+ motor.init();

+ // align encoder and start FOC

+ motor.initFOC();

+

+ // add target command T

+ command.add('T', doTarget, "target angle");

+

+ Serial.println(F("Motor ready."));

+ Serial.println(F("Set the target angle using serial terminal:"));

+ _delay(1000);

+}

+

+void loop() {

+ // main FOC algorithm function

+ // the faster you run this function the better

+ // Arduino UNO loop ~1kHz

+ // Bluepill loop ~10kHz

+ motor.loopFOC();

+

+ // Motion control function

+ // velocity, position or voltage (defined in motor.controller)

+ // this function can be run at much lower frequency than loopFOC() function

+ // You can also use motor.move() and set the motor.target in the code

+ motor.move(target_angle);

+

+ // function intended to be used with serial plotter to monitor motor variables

+ // significantly slowing the execution down!!!!

+ // motor.monitor();

+

+ // user communication

+ command.run();

+}

\ No newline at end of file

diff --git a/embedded/CANFDMigrate/.pio/libdeps/seeed_xiao_esp32s3/Simple FOC/examples/hardware_specific_examples/Bluepill_examples/magnetic_sensor/bluepill_position_control/bluepill_position_control.ino b/embedded/CANFDMigrate/.pio/libdeps/seeed_xiao_esp32s3/Simple FOC/examples/hardware_specific_examples/Bluepill_examples/magnetic_sensor/bluepill_position_control/bluepill_position_control.ino

new file mode 100644

index 0000000..caef7ff

--- /dev/null

+++ b/embedded/CANFDMigrate/.pio/libdeps/seeed_xiao_esp32s3/Simple FOC/examples/hardware_specific_examples/Bluepill_examples/magnetic_sensor/bluepill_position_control/bluepill_position_control.ino

@@ -0,0 +1,119 @@

+/**

+ *

+ * STM32 Bluepill position motion control example with magnetic sensor

+ *

+ * The same example can be ran with any STM32 board - just make sure that put right pin numbers.

+ *

+ */

+#include

+

+// SPI Magnetic sensor instance (AS5047U example)

+// MISO PA7

+// MOSI PA6

+// SCK PA5

+MagneticSensorSPI sensor = MagneticSensorSPI(PA4, 14, 0x3FFF);

+

+// I2C Magnetic sensor instance (AS5600 example)

+// make sure to use the pull-ups!!

+// SDA PB7

+// SCL PB6

+//MagneticSensorI2C sensor = MagneticSensorI2C(0x36, 12, 0X0C, 4);

+

+// Motor instance

+BLDCMotor motor = BLDCMotor(11);

+// BLDCDriver3PWM(IN1, IN2, IN3, enable(optional))

+BLDCDriver3PWM driver = BLDCDriver3PWM(PB6, PB7, PB8, PB5);

+// BLDCDriver6PWM(IN1_H, IN1_L, IN2_H, IN2_L, IN3_H, IN3_L, enable(optional))

+//BLDCDriver6PWM driver = BLDCDriver6PWM(PA8, PB13, PA9, PB14, PA10, PB15, PB12);

+

+

+// angle set point variable

+float target_angle = 0;

+// instantiate the commander

+Commander command = Commander(Serial);

+void doTarget(char* cmd) { command.scalar(&target_angle, cmd); }

+

+

+void setup() {

+

+ // use monitoring with serial

+ Serial.begin(115200);

+ // enable more verbose output for debugging

+ // comment out if not needed

+ SimpleFOCDebug::enable(&Serial);

+

+ // initialise magnetic sensor hardware

+ sensor.init();

+ // link the motor to the sensor

+ motor.linkSensor(&sensor);

+

+ // driver config

+ // power supply voltage [V]

+ driver.voltage_power_supply = 12;

+ driver.init();

+ // link the motor and the driver

+ motor.linkDriver(&driver);

+

+ // choose FOC modulation (optional)

+ motor.foc_modulation = FOCModulationType::SpaceVectorPWM;

+

+ // set motion control loop to be used

+ motor.controller = MotionControlType::angle;

+

+ // contoller configuration

+ // default parameters in defaults.h

+

+ // velocity PI controller parameters

+ motor.PID_velocity.P = 0.2f;

+ motor.PID_velocity.I = 20;

+ // maximal voltage to be set to the motor

+ motor.voltage_limit = 6;

+

+ // velocity low pass filtering time constant

+ // the lower the less filtered

+ motor.LPF_velocity.Tf = 0.01f;

+

+ // angle P controller

+ motor.P_angle.P = 20;

+ // maximal velocity of the position control

+ motor.velocity_limit = 40;

+

+ // comment out if not needed

+ motor.useMonitoring(Serial);

+

+

+ // initialize motor

+ motor.init();

+ // align sensor and start FOC

+ motor.initFOC();

+

+ // add target command T

+ command.add('T', doTarget, "target angle");

+

+ Serial.println(F("Motor ready."));

+ Serial.println(F("Set the target angle using serial terminal:"));

+ _delay(1000);

+}

+

+void loop() {

+

+ // main FOC algorithm function

+ // the faster you run this function the better

+ // Arduino UNO loop ~1kHz

+ // Bluepill loop ~10kHz

+ motor.loopFOC();

+

+ // Motion control function

+ // velocity, position or voltage (defined in motor.controller)

+ // this function can be run at much lower frequency than loopFOC() function

+ // You can also use motor.move() and set the motor.target in the code

+ motor.move(target_angle);

+

+

+ // function intended to be used with serial plotter to monitor motor variables

+ // significantly slowing the execution down!!!!

+ // motor.monitor();

+

+ // user communication

+ command.run();

+}

\ No newline at end of file

diff --git a/embedded/CANFDMigrate/.pio/libdeps/seeed_xiao_esp32s3/Simple FOC/examples/hardware_specific_examples/DRV8302_driver/3pwm_example/encoder/full_control_serial/full_control_serial.ino b/embedded/CANFDMigrate/.pio/libdeps/seeed_xiao_esp32s3/Simple FOC/examples/hardware_specific_examples/DRV8302_driver/3pwm_example/encoder/full_control_serial/full_control_serial.ino

new file mode 100644

index 0000000..3d90db1

--- /dev/null

+++ b/embedded/CANFDMigrate/.pio/libdeps/seeed_xiao_esp32s3/Simple FOC/examples/hardware_specific_examples/DRV8302_driver/3pwm_example/encoder/full_control_serial/full_control_serial.ino

@@ -0,0 +1,133 @@

+/**

+ * Comprehensive BLDC motor control example using encoder and the DRV8302 board

+ *

+ * Using serial terminal user can send motor commands and configure the motor and FOC in real-time:

+ * - configure PID controller constants

+ * - change motion control loops

+ * - monitor motor variabels

+ * - set target values

+ * - check all the configuration values

+ *

+ * check the https://docs.simplefoc.com for full list of motor commands

+ *

+ */

+#include

+

+// DRV8302 pins connections

+// don't forget to connect the common ground pin

+#define INH_A 9

+#define INH_B 10

+#define INH_C 11

+

+#define EN_GATE 7

+#define M_PWM A1

+#define M_OC A2

+#define OC_ADJ A3

+

+// Motor instance

+BLDCMotor motor = BLDCMotor(11);

+BLDCDriver3PWM driver = BLDCDriver3PWM(INH_A, INH_B, INH_C, EN_GATE);

+

+// encoder instance

+Encoder encoder = Encoder(2, 3, 8192);

+

+// Interrupt routine intialisation

+// channel A and B callbacks

+void doA(){encoder.handleA();}

+void doB(){encoder.handleB();}

+

+

+// commander interface

+Commander command = Commander(Serial);

+void onMotor(char* cmd){ command.motor(&motor, cmd); }

+

+void setup() {

+

+ // use monitoring with serial

+ Serial.begin(115200);

+ // enable more verbose output for debugging

+ // comment out if not needed

+ SimpleFOCDebug::enable(&Serial);

+

+ // initialize encoder sensor hardware

+ encoder.init();

+ encoder.enableInterrupts(doA, doB);

+ // link the motor to the sensor

+ motor.linkSensor(&encoder);

+

+ // DRV8302 specific code

+ // M_OC - enable overcurrent protection

+ pinMode(M_OC,OUTPUT);

+ digitalWrite(M_OC,LOW);

+ // M_PWM - enable 3pwm mode

+ pinMode(M_PWM,OUTPUT);

+ digitalWrite(M_PWM,HIGH);

+ // OD_ADJ - set the maximum overcurrent limit possible

+ // Better option would be to use voltage divisor to set exact value

+ pinMode(OC_ADJ,OUTPUT);

+ digitalWrite(OC_ADJ,HIGH);

+

+

+ // driver config

+ // power supply voltage [V]

+ driver.voltage_power_supply = 12;

+ driver.init();

+ // link the motor and the driver

+ motor.linkDriver(&driver);

+

+

+ // choose FOC modulation

+ motor.foc_modulation = FOCModulationType::SpaceVectorPWM;

+

+ // set control loop type to be used

+ motor.controller = MotionControlType::torque;

+

+ // contoller configuration based on the controll type

+ motor.PID_velocity.P = 0.2f;

+ motor.PID_velocity.I = 20;

+ // default voltage_power_supply

+ motor.voltage_limit = 12;

+

+ // velocity low pass filtering time constant

+ motor.LPF_velocity.Tf = 0.01f;

+

+ // angle loop controller

+ motor.P_angle.P = 20;

+ // angle loop velocity limit

+ motor.velocity_limit = 50;

+

+ // comment out if not needed

+ motor.useMonitoring(Serial);

+

+ // initialise motor

+ motor.init();

+ // align encoder and start FOC

+ motor.initFOC();

+

+ // set the inital target value

+ motor.target = 2;

+

+ // define the motor id

+ command.add('A', onMotor, "motor");

+

+ Serial.println(F("Full control example: "));

+ Serial.println(F("Run user commands to configure and the motor (find the full command list in docs.simplefoc.com) \n "));

+ Serial.println(F("Initial motion control loop is voltage loop."));

+ Serial.println(F("Initial target voltage 2V."));

+

+ _delay(1000);

+}

+

+

+void loop() {

+ // iterative setting FOC phase voltage

+ motor.loopFOC();

+

+ // iterative function setting the outter loop target

+ // velocity, position or voltage

+ // if tatget not set in parameter uses motor.target variable

+ motor.move();

+

+ // user communication

+ command.run();

+}

\ No newline at end of file

diff --git a/embedded/CANFDMigrate/.pio/libdeps/seeed_xiao_esp32s3/Simple FOC/examples/hardware_specific_examples/DRV8302_driver/6pwm_example/encoder/full_control_serial/full_control_serial.ino b/embedded/CANFDMigrate/.pio/libdeps/seeed_xiao_esp32s3/Simple FOC/examples/hardware_specific_examples/DRV8302_driver/6pwm_example/encoder/full_control_serial/full_control_serial.ino

new file mode 100644

index 0000000..af56e06

--- /dev/null

+++ b/embedded/CANFDMigrate/.pio/libdeps/seeed_xiao_esp32s3/Simple FOC/examples/hardware_specific_examples/DRV8302_driver/6pwm_example/encoder/full_control_serial/full_control_serial.ino

@@ -0,0 +1,132 @@

+/**

+ * Comprehensive BLDC motor control example using encoder and the DRV8302 board

+ *

+ * Using serial terminal user can send motor commands and configure the motor and FOC in real-time:

+ * - configure PID controller constants

+ * - change motion control loops

+ * - monitor motor variabels

+ * - set target values

+ * - check all the configuration values

+ *

+ * check the https://docs.simplefoc.com for full list of motor commands

+ *

+ */

+#include

+

+// DRV8302 pins connections

+// don't forget to connect the common ground pin

+#define INH_A 3

+#define INH_B 5

+#define INH_C 9

+#define INL_A 11

+#define INL_B 6

+#define INL_C 10

+

+#define EN_GATE 7

+#define M_PWM A1

+#define M_OC A2

+#define OC_ADJ A3

+

+// Motor instance

+BLDCMotor motor = BLDCMotor(11);

+BLDCDriver6PWM driver = BLDCDriver6PWM(INH_A,INL_A, INH_B,INL_B, INH_C,INL_C, EN_GATE);

+

+// encoder instance

+Encoder encoder = Encoder(2, 3, 8192);

+

+// Interrupt routine intialisation

+// channel A and B callbacks

+void doA(){encoder.handleA();}

+void doB(){encoder.handleB();}

+

+

+// commander interface

+Commander command = Commander(Serial);

+void onMotor(char* cmd){ command.motor(&motor, cmd); }

+

+void setup() {

+

+ // use monitoring with serial

+ Serial.begin(115200);

+ // enable more verbose output for debugging

+ // comment out if not needed

+ SimpleFOCDebug::enable(&Serial);

+

+ // initialize encoder sensor hardware

+ encoder.init();

+ encoder.enableInterrupts(doA, doB);

+ // link the motor to the sensor

+ motor.linkSensor(&encoder);

+

+ // DRV8302 specific code

+ // M_OC - enable overcurrent protection

+ pinMode(M_OC,OUTPUT);

+ digitalWrite(M_OC,LOW);

+ // M_PWM - disable 3pwm mode

+ pinMode(M_PWM,OUTPUT);

+ digitalWrite(M_PWM, LOW);

+ // OD_ADJ - set the maximum overcurrent limit possible

+ // Better option would be to use voltage divisor to set exact value

+ pinMode(OC_ADJ,OUTPUT);

+ digitalWrite(OC_ADJ,HIGH);

+

+ // driver config

+ // power supply voltage [V]

+ driver.voltage_power_supply = 12;

+ driver.init();

+ // link the motor and the driver

+ motor.linkDriver(&driver);

+

+ // choose FOC modulation

+ motor.foc_modulation = FOCModulationType::SpaceVectorPWM;

+

+ // set control loop type to be used

+ motor.controller = MotionControlType::torque;

+

+ // contoller configuration based on the controll type

+ motor.PID_velocity.P = 0.2f;

+ motor.PID_velocity.I = 20;

+ // default voltage_power_supply

+ motor.voltage_limit = 12;

+

+ // velocity low pass filtering time constant

+ motor.LPF_velocity.Tf = 0.01f;

+

+ // angle loop controller

+ motor.P_angle.P = 20;

+ // angle loop velocity limit

+ motor.velocity_limit = 50;

+

+ // comment out if not needed

+ motor.useMonitoring(Serial);

+

+ // initialise motor

+ motor.init();

+ // align encoder and start FOC

+ motor.initFOC();

+

+ // set the inital target value

+ motor.target = 2;

+

+ // define the motor id

+ command.add('M', onMotor, "motor");

+

+ Serial.println(F("Initial motion control loop is voltage loop."));

+ Serial.println(F("Initial target voltage 2V."));

+

+ _delay(1000);

+}

+

+

+void loop() {

+ // iterative setting FOC phase voltage

+ motor.loopFOC();

+

+ // iterative function setting the outter loop target

+ // velocity, position or voltage

+ // if tatget not set in parameter uses motor.target variable

+ motor.move();

+

+ // user communication

+ command.run();

+}

diff --git a/embedded/CANFDMigrate/.pio/libdeps/seeed_xiao_esp32s3/Simple FOC/examples/hardware_specific_examples/DRV8302_driver/esp32_current_control_low_side/esp32_current_control_low_side.ino b/embedded/CANFDMigrate/.pio/libdeps/seeed_xiao_esp32s3/Simple FOC/examples/hardware_specific_examples/DRV8302_driver/esp32_current_control_low_side/esp32_current_control_low_side.ino

new file mode 100644

index 0000000..7d7fe14

--- /dev/null

+++ b/embedded/CANFDMigrate/.pio/libdeps/seeed_xiao_esp32s3/Simple FOC/examples/hardware_specific_examples/DRV8302_driver/esp32_current_control_low_side/esp32_current_control_low_side.ino

@@ -0,0 +1,169 @@

+/**

+ * Comprehensive BLDC motor control example using encoder and the DRV8302 board

+ *

+ * Using serial terminal user can send motor commands and configure the motor and FOC in real-time:

+ * - configure PID controller constants

+ * - change motion control loops

+ * - monitor motor variabels

+ * - set target values

+ * - check all the configuration values

+ *

+ * check the https://docs.simplefoc.com for full list of motor commands

+ *

+ */

+#include

+

+// DRV8302 pins connections

+// don't forget to connect the common ground pin

+#define INH_A 21

+#define INH_B 19

+#define INH_C 18

+

+#define EN_GATE 5

+#define M_PWM 25

+#define M_OC 26

+#define OC_ADJ 12

+#define OC_GAIN 14

+

+#define IOUTA 34

+#define IOUTB 35

+#define IOUTC 32

+

+// Motor instance

+BLDCMotor motor = BLDCMotor(7);

+BLDCDriver3PWM driver = BLDCDriver3PWM(INH_A, INH_B, INH_C, EN_GATE);

+

+// DRV8302 board has 0.005Ohm shunt resistors and the gain of 12.22 V/V

+LowsideCurrentSense cs = LowsideCurrentSense(0.005f, 12.22f, IOUTA, IOUTB, IOUTC);

+

+// encoder instance

+Encoder encoder = Encoder(22, 23, 500);

+

+// Interrupt routine intialisation

+// channel A and B callbacks

+void doA(){encoder.handleA();}

+void doB(){encoder.handleB();}

+

+

+// commander interface

+Commander command = Commander(Serial);

+void onMotor(char* cmd){ command.motor(&motor, cmd); }

+

+void setup() {

+

+ // use monitoring with serial

+ Serial.begin(115200);

+ // enable more verbose output for debugging

+ // comment out if not needed

+ SimpleFOCDebug::enable(&Serial);

+

+ // initialize encoder sensor hardware

+ encoder.init();

+ encoder.enableInterrupts(doA, doB);

+ // link the motor to the sensor

+ motor.linkSensor(&encoder);

+

+ // DRV8302 specific code

+ // M_OC - enable overcurrent protection

+ pinMode(M_OC,OUTPUT);

+ digitalWrite(M_OC,LOW);

+ // M_PWM - enable 3pwm mode

+ pinMode(M_PWM,OUTPUT);

+ digitalWrite(M_PWM,HIGH);

+ // OD_ADJ - set the maximum overcurrent limit possible

+ // Better option would be to use voltage divisor to set exact value

+ pinMode(OC_ADJ,OUTPUT);

+ digitalWrite(OC_ADJ,HIGH);

+ pinMode(OC_GAIN,OUTPUT);

+ digitalWrite(OC_GAIN,LOW);

+

+

+ // driver config

+ // power supply voltage [V]

+ driver.voltage_power_supply = 12;

+ driver.pwm_frequency = 15000;

+ driver.init();

+ // link the motor and the driver

+ motor.linkDriver(&driver);

+ // link current sense and the driver

+ cs.linkDriver(&driver);

+

+ // align voltage

+ motor.voltage_sensor_align = 0.5;

+

+ // control loop type and torque mode

+ motor.torque_controller = TorqueControlType::voltage;

+ motor.controller = MotionControlType::torque;

+ motor.motion_downsample = 0.0;

+

+ // velocity loop PID

+ motor.PID_velocity.P = 0.2;

+ motor.PID_velocity.I = 5.0;

+ // Low pass filtering time constant

+ motor.LPF_velocity.Tf = 0.02;

+ // angle loop PID

+ motor.P_angle.P = 20.0;

+ // Low pass filtering time constant

+ motor.LPF_angle.Tf = 0.0;

+ // current q loop PID

+ motor.PID_current_q.P = 3.0;

+ motor.PID_current_q.I = 100.0;

+ // Low pass filtering time constant

+ motor.LPF_current_q.Tf = 0.02;

+ // current d loop PID

+ motor.PID_current_d.P = 3.0;

+ motor.PID_current_d.I = 100.0;

+ // Low pass filtering time constant

+ motor.LPF_current_d.Tf = 0.02;

+

+ // Limits

+ motor.velocity_limit = 100.0; // 100 rad/s velocity limit

+ motor.voltage_limit = 12.0; // 12 Volt limit

+ motor.current_limit = 2.0; // 2 Amp current limit

+

+ // comment out if not needed

+ motor.useMonitoring(Serial);

+ motor.monitor_variables = _MON_CURR_Q | _MON_CURR_D; // monitor the two currents d and q

+ motor.monitor_downsample = 1000;

+

+ // initialise motor

+ motor.init();

+

+ cs.init();

+ // driver 8302 has inverted gains on all channels

+ cs.gain_a *=-1;

+ cs.gain_b *=-1;

+ cs.gain_c *=-1;

+ motor.linkCurrentSense(&cs);

+

+ // align encoder and start FOC

+ motor.initFOC();

+

+ // set the inital target value

+ motor.target = 0;

+

+ // define the motor id

+ command.add('M', onMotor, "motor");

+

+ Serial.println(F("Full control example: "));

+ Serial.println(F("Run user commands to configure and the motor (find the full command list in docs.simplefoc.com) \n "));

+ Serial.println(F("Initial motion control loop is voltage loop."));

+ Serial.println(F("Initial target voltage 2V."));

+

+ _delay(1000);

+}

+

+

+void loop() {

+ // iterative setting FOC phase voltage

+ motor.loopFOC();

+

+ // iterative function setting the outter loop target

+ motor.move();

+

+ // monitoring the state variables

+ motor.monitor();

+

+ // user communication

+ command.run();

+}

\ No newline at end of file

diff --git a/embedded/CANFDMigrate/.pio/libdeps/seeed_xiao_esp32s3/Simple FOC/examples/hardware_specific_examples/DRV8302_driver/stm32_current_control_low_side/stm32_current_control_low_side.ino b/embedded/CANFDMigrate/.pio/libdeps/seeed_xiao_esp32s3/Simple FOC/examples/hardware_specific_examples/DRV8302_driver/stm32_current_control_low_side/stm32_current_control_low_side.ino

new file mode 100644

index 0000000..e1b4c39

--- /dev/null

+++ b/embedded/CANFDMigrate/.pio/libdeps/seeed_xiao_esp32s3/Simple FOC/examples/hardware_specific_examples/DRV8302_driver/stm32_current_control_low_side/stm32_current_control_low_side.ino

@@ -0,0 +1,169 @@

+/**

+ * Comprehensive BLDC motor control example using encoder and the DRV8302 board

+ *

+ * Using serial terminal user can send motor commands and configure the motor and FOC in real-time:

+ * - configure PID controller constants

+ * - change motion control loops

+ * - monitor motor variabels

+ * - set target values

+ * - check all the configuration values

+ *

+ * check the https://docs.simplefoc.com for full list of motor commands

+ *

+ */

+#include

+

+// DRV8302 pins connections

+// don't forget to connect the common ground pin

+#define INH_A PA8

+#define INH_B PA9

+#define INH_C PA10

+

+#define EN_GATE PB7

+#define M_PWM PB4

+#define M_OC PB3

+#define OC_ADJ PB6

+#define OC_GAIN PB5

+

+#define IOUTA PA0

+#define IOUTB PA1

+#define IOUTC PA2

+

+// Motor instance

+BLDCMotor motor = BLDCMotor(7);

+BLDCDriver3PWM driver = BLDCDriver3PWM(INH_A, INH_B, INH_C, EN_GATE);

+

+// DRV8302 board has 0.005Ohm shunt resistors and the gain of 12.22 V/V

+LowsideCurrentSense cs = LowsideCurrentSense(0.005f, 12.22f, IOUTA, IOUTB, IOUTC);

+

+// encoder instance

+Encoder encoder = Encoder(PB14, PB15, 2048);

+

+// Interrupt routine intialisation

+// channel A and B callbacks

+void doA(){encoder.handleA();}

+void doB(){encoder.handleB();}

+

+

+// commander interface

+Commander command = Commander(Serial);

+void onMotor(char* cmd){ command.motor(&motor, cmd); }

+

+void setup() {

+

+ // use monitoring with serial

+ Serial.begin(115200);

+ // enable more verbose output for debugging

+ // comment out if not needed

+ SimpleFOCDebug::enable(&Serial);

+

+ // initialize encoder sensor hardware

+ encoder.init();

+ encoder.enableInterrupts(doA, doB);

+ // link the motor to the sensor

+ motor.linkSensor(&encoder);

+

+ // DRV8302 specific code

+ // M_OC - enable overcurrent protection

+ pinMode(M_OC,OUTPUT);

+ digitalWrite(M_OC,LOW);

+ // M_PWM - enable 3pwm mode

+ pinMode(M_PWM,OUTPUT);

+ digitalWrite(M_PWM,HIGH);

+ // OD_ADJ - set the maximum overcurrent limit possible

+ // Better option would be to use voltage divisor to set exact value

+ pinMode(OC_ADJ,OUTPUT);

+ digitalWrite(OC_ADJ,HIGH);

+ pinMode(OC_GAIN,OUTPUT);

+ digitalWrite(OC_GAIN,LOW);

+

+

+ // driver config

+ // power supply voltage [V]

+ driver.voltage_power_supply = 19;

+ driver.pwm_frequency = 15000; // suggested under 18khz

+ driver.init();

+ // link the motor and the driver

+ motor.linkDriver(&driver);

+ // link current sense and the driver

+ cs.linkDriver(&driver);

+

+ // align voltage

+ motor.voltage_sensor_align = 0.5;

+

+ // control loop type and torque mode

+ motor.torque_controller = TorqueControlType::voltage;

+ motor.controller = MotionControlType::torque;

+ motor.motion_downsample = 0.0;

+

+ // velocity loop PID

+ motor.PID_velocity.P = 0.2;

+ motor.PID_velocity.I = 5.0;

+ // Low pass filtering time constant

+ motor.LPF_velocity.Tf = 0.02;

+ // angle loop PID

+ motor.P_angle.P = 20.0;

+ // Low pass filtering time constant

+ motor.LPF_angle.Tf = 0.0;

+ // current q loop PID

+ motor.PID_current_q.P = 3.0;

+ motor.PID_current_q.I = 100.0;

+ // Low pass filtering time constant

+ motor.LPF_current_q.Tf = 0.02;

+ // current d loop PID

+ motor.PID_current_d.P = 3.0;

+ motor.PID_current_d.I = 100.0;

+ // Low pass filtering time constant

+ motor.LPF_current_d.Tf = 0.02;

+

+ // Limits

+ motor.velocity_limit = 100.0; // 100 rad/s velocity limit

+ motor.voltage_limit = 12.0; // 12 Volt limit

+ motor.current_limit = 2.0; // 2 Amp current limit

+

+ // comment out if not needed

+ motor.useMonitoring(Serial);

+ motor.monitor_variables = _MON_CURR_Q | _MON_CURR_D; // monitor the two currents d and q

+ motor.monitor_downsample = 0;

+

+ // initialise motor

+ motor.init();

+

+ cs.init();

+ // driver 8302 has inverted gains on all channels

+ cs.gain_a *=-1;

+ cs.gain_b *=-1;

+ cs.gain_c *=-1;

+ motor.linkCurrentSense(&cs);

+

+ // align encoder and start FOC

+ motor.initFOC();

+

+ // set the inital target value

+ motor.target = 0;

+

+ // define the motor id

+ command.add('M', onMotor, "motor");

+

+ Serial.println(F("Full control example: "));

+ Serial.println(F("Run user commands to configure and the motor (find the full command list in docs.simplefoc.com) \n "));

+ Serial.println(F("Initial motion control loop is voltage loop."));

+ Serial.println(F("Initial target voltage 2V."));

+

+ _delay(1000);

+}

+

+

+void loop() {

+ // iterative setting FOC phase voltage

+ motor.loopFOC();

+

+ // iterative function setting the outter loop target

+ motor.move();

+

+ // monitoring the state variables

+ motor.monitor();

+

+ // user communication

+ command.run();

+}

\ No newline at end of file

diff --git a/embedded/CANFDMigrate/.pio/libdeps/seeed_xiao_esp32s3/Simple FOC/examples/hardware_specific_examples/DRV8302_driver/teensy4_current_control_low_side/teensy4_current_control_low_side.ino b/embedded/CANFDMigrate/.pio/libdeps/seeed_xiao_esp32s3/Simple FOC/examples/hardware_specific_examples/DRV8302_driver/teensy4_current_control_low_side/teensy4_current_control_low_side.ino

new file mode 100644

index 0000000..c9b4516

--- /dev/null

+++ b/embedded/CANFDMigrate/.pio/libdeps/seeed_xiao_esp32s3/Simple FOC/examples/hardware_specific_examples/DRV8302_driver/teensy4_current_control_low_side/teensy4_current_control_low_side.ino

@@ -0,0 +1,170 @@

+/**

+ * Comprehensive BLDC motor control example using encoder and the DRV8302 board

+ *

+ * Using serial terminal user can send motor commands and configure the motor and FOC in real-time:

+ * - configure PID controller constants

+ * - change motion control loops

+ * - monitor motor variabels

+ * - set target values

+ * - check all the configuration values

+ *

+ * check the https://docs.simplefoc.com for full list of motor commands

+ *

+ */

+#include

+

+// DRV8302 pins connections

+// don't forget to connect the common ground pin

+#define EN_GATE 11

+#define M_PWM 22

+#define GAIN 20

+#define M_OC 23

+#define OC_ADJ 19

+

+#define INH_A 2

+#define INL_A 3

+#define INH_B 8

+#define INL_B 7

+#define INH_C 6

+#define INL_C 9

+

+#define IOUTA 14

+#define IOUTB 15

+#define IOUTC 16

+

+// Motor instance

+BLDCMotor motor = BLDCMotor(7);

+BLDCDriver3PWM driver = BLDCDriver3PWM(INH_A, INH_B, INH_C, EN_GATE);

+

+// DRV8302 board has 0.005Ohm shunt resistors and the gain of 12.22 V/V

+LowsideCurrentSense cs = LowsideCurrentSense(0.005f, 12.22f, IOUTA, IOUTB);

+

+// encoder instance

+Encoder encoder = Encoder(10, 11, 2048);

+

+// Interrupt routine intialisation

+// channel A and B callbacks

+void doA(){encoder.handleA();}

+void doB(){encoder.handleB();}

+

+

+// commander interface

+Commander command = Commander(Serial);

+void onMotor(char* cmd){ command.motor(&motor, cmd); }

+

+void setup() {

+

+ // use monitoring with serial

+ Serial.begin(115200);

+ // enable more verbose output for debugging

+ // comment out if not needed

+ SimpleFOCDebug::enable(&Serial);

+

+ // initialize encoder sensor hardware

+ encoder.init();

+ encoder.enableInterrupts(doA, doB);

+ // link the motor to the sensor

+ motor.linkSensor(&encoder);

+

+ // DRV8302 specific code

+ // M_OC - enable overcurrent protection

+ pinMode(M_OC,OUTPUT);

+ digitalWrite(M_OC,LOW);

+ // M_PWM - enable 6pwm mode

+ pinMode(M_PWM, OUTPUT);

+ digitalWrite(M_PWM,LOW); // high for 3pwm

+ // OD_ADJ - set the maximum overcurrent limit possible

+ // Better option would be to use voltage divisor to set exact value

+ pinMode(OC_ADJ,OUTPUT);

+ digitalWrite(OC_ADJ,HIGH);

+

+

+ // driver config

+ // power supply voltage [V]

+ driver.voltage_power_supply = 19;

+ driver.pwm_frequency = 20000; // suggested not higher than 22khz

+ driver.init();

+ // link the motor and the driver

+ motor.linkDriver(&driver);

+ // link current sense and the driver

+ cs.linkDriver(&driver);

+

+ // align voltage

+ motor.voltage_sensor_align = 0.5;

+

+ // control loop type and torque mode

+ motor.torque_controller = TorqueControlType::voltage;

+ motor.controller = MotionControlType::torque;

+ motor.motion_downsample = 0.0;

+

+ // velocity loop PID

+ motor.PID_velocity.P = 0.2;

+ motor.PID_velocity.I = 5.0;

+ // Low pass filtering time constant

+ motor.LPF_velocity.Tf = 0.02;

+ // angle loop PID

+ motor.P_angle.P = 20.0;

+ // Low pass filtering time constant

+ motor.LPF_angle.Tf = 0.0;

+ // current q loop PID

+ motor.PID_current_q.P = 3.0;

+ motor.PID_current_q.I = 100.0;

+ // Low pass filtering time constant

+ motor.LPF_current_q.Tf = 0.02;

+ // current d loop PID

+ motor.PID_current_d.P = 3.0;

+ motor.PID_current_d.I = 100.0;

+ // Low pass filtering time constant

+ motor.LPF_current_d.Tf = 0.02;

+

+ // Limits

+ motor.velocity_limit = 100.0; // 100 rad/s velocity limit

+ motor.voltage_limit = 12.0; // 12 Volt limit

+ motor.current_limit = 2.0; // 2 Amp current limit

+

+ // comment out if not needed

+ motor.useMonitoring(Serial);

+ motor.monitor_variables = _MON_CURR_Q | _MON_CURR_D; // monitor the two currents d and q

+ motor.monitor_downsample = 0;

+

+ // initialise motor

+ motor.init();

+

+ cs.init();

+ // driver 8302 has inverted gains on all channels

+ cs.gain_a *=-1;

+ cs.gain_b *=-1;

+ cs.gain_c *=-1;

+ motor.linkCurrentSense(&cs);

+

+ // align encoder and start FOC

+ motor.initFOC();

+

+ // set the inital target value

+ motor.target = 0;

+

+ // define the motor id

+ command.add('M', onMotor, "motor");

+

+ Serial.println(F("Full control example: "));

+ Serial.println(F("Run user commands to configure and the motor (find the full command list in docs.simplefoc.com) \n "));

+ Serial.println(F("Initial motion control loop is voltage loop."));

+ Serial.println(F("Initial target voltage 2V."));

+

+ _delay(1000);

+}

+

+

+void loop() {

+ // iterative setting FOC phase voltage

+ motor.loopFOC();

+

+ // iterative function setting the outter loop target

+ motor.move();

+

+ // monitoring the state variables

+ motor.monitor();

+

+ // user communication

+ command.run();

+}

\ No newline at end of file

diff --git a/embedded/CANFDMigrate/.pio/libdeps/seeed_xiao_esp32s3/Simple FOC/examples/hardware_specific_examples/ESP32/encoder/esp32_position_control/esp32_position_control.ino b/embedded/CANFDMigrate/.pio/libdeps/seeed_xiao_esp32s3/Simple FOC/examples/hardware_specific_examples/ESP32/encoder/esp32_position_control/esp32_position_control.ino

new file mode 100644

index 0000000..7f6b33c

--- /dev/null

+++ b/embedded/CANFDMigrate/.pio/libdeps/seeed_xiao_esp32s3/Simple FOC/examples/hardware_specific_examples/ESP32/encoder/esp32_position_control/esp32_position_control.ino

@@ -0,0 +1,110 @@

+/**

+ * ESP32 position motion control example with encoder

+ *

+ */

+#include

+

+// Motor instance

+BLDCMotor motor = BLDCMotor(11);

+BLDCDriver3PWM driver = BLDCDriver3PWM(25, 26, 27, 7);

+

+// encoder instance

+Encoder encoder = Encoder(4, 2, 1024);

+

+// Interrupt routine intialisation

+// channel A and B callbacks

+void doA(){encoder.handleA();}

+void doB(){encoder.handleB();}

+

+// angle set point variable

+float target_angle = 0;

+// instantiate the commander

+Commander command = Commander(Serial);

+void doTarget(char* cmd) { command.scalar(&target_angle, cmd); }

+

+void setup() {

+

+ // use monitoring with serial

+ Serial.begin(115200);

+ // enable more verbose output for debugging

+ // comment out if not needed

+ SimpleFOCDebug::enable(&Serial);

+

+ // initialize encoder sensor hardware

+ encoder.init();

+ encoder.enableInterrupts(doA, doB);

+

+ // link the motor to the sensor

+ motor.linkSensor(&encoder);

+

+ // driver config

+ // power supply voltage [V]

+ driver.voltage_power_supply = 12;

+ driver.init();

+ // link the motor and the driver

+ motor.linkDriver(&driver);

+

+ // aligning voltage [V]

+ motor.voltage_sensor_align = 3;

+ // index search velocity [rad/s]

+ motor.velocity_index_search = 3;

+

+ // set motion control loop to be used

+ motor.controller = MotionControlType::velocity;

+

+ // contoller configuration

+ // default parameters in defaults.h

+

+ // velocity PI controller parameters

+ motor.PID_velocity.P = 0.2f;

+ motor.PID_velocity.I = 20;

+ // default voltage_power_supply

+ motor.voltage_limit = 6;

+ // jerk control using voltage voltage ramp

+ // default value is 300 volts per sec ~ 0.3V per millisecond

+ motor.PID_velocity.output_ramp = 1000;

+

+ // velocity low pass filtering time constant

+ motor.LPF_velocity.Tf = 0.01f;

+

+ // angle P controller

+ motor.P_angle.P = 20;

+ // maximal velocity of the position control

+ motor.velocity_limit = 4;

+

+ // comment out if not needed

+ motor.useMonitoring(Serial);

+

+ // initialize motor

+ motor.init();

+ // align encoder and start FOC

+ motor.initFOC();

+

+ // add target command T

+ command.add('T', doTarget, "target angle");

+

+ Serial.println(F("Motor ready."));

+ Serial.println(F("Set the target angle using serial terminal:"));

+ _delay(1000);

+}

+

+void loop() {

+ // main FOC algorithm function

+ // the faster you run this function the better

+ // Arduino UNO loop ~1kHz

+ // Bluepill loop ~10kHz

+ motor.loopFOC();

+

+ // Motion control function

+ // velocity, position or voltage (defined in motor.controller)

+ // this function can be run at much lower frequency than loopFOC() function

+ // You can also use motor.move() and set the motor.target in the code

+ motor.move(target_angle);

+

+ // function intended to be used with serial plotter to monitor motor variables

+ // significantly slowing the execution down!!!!

+ // motor.monitor();

+

+ // user communication

+ command.run();

+}

\ No newline at end of file

diff --git a/embedded/CANFDMigrate/.pio/libdeps/seeed_xiao_esp32s3/Simple FOC/examples/hardware_specific_examples/ESP32/magnetic_sensor/esp32_position_control/esp32_position_control.ino b/embedded/CANFDMigrate/.pio/libdeps/seeed_xiao_esp32s3/Simple FOC/examples/hardware_specific_examples/ESP32/magnetic_sensor/esp32_position_control/esp32_position_control.ino

new file mode 100644

index 0000000..9ba9604

--- /dev/null

+++ b/embedded/CANFDMigrate/.pio/libdeps/seeed_xiao_esp32s3/Simple FOC/examples/hardware_specific_examples/ESP32/magnetic_sensor/esp32_position_control/esp32_position_control.ino

@@ -0,0 +1,116 @@

+/**

+ * ESP32 position motion control example with magnetic sensor

+ */

+#include

+

+// SPI Magnetic sensor instance (AS5047U example)

+// MISO 12

+// MOSI 9

+// SCK 14

+// magnetic sensor instance - SPI

+MagneticSensorSPI sensor = MagneticSensorSPI(AS5147_SPI, 15);

+

+// I2C Magnetic sensor instance (AS5600 example)

+// make sure to use the pull-ups!!

+// SDA 21

+// SCL 22

+// magnetic sensor instance - I2C

+//MagneticSensorI2C sensor = MagneticSensorI2C(AS5600_I2C);

+

+// Analog output Magnetic sensor instance (AS5600)

+// MagneticSensorAnalog sensor = MagneticSensorAnalog(A1, 14, 1020);

+

+// Motor instance

+BLDCMotor motor = BLDCMotor(11);

+BLDCDriver3PWM driver = BLDCDriver3PWM(25, 26, 27, 7);

+

+

+// angle set point variable

+float target_angle = 0;

+// instantiate the commander

+Commander command = Commander(Serial);

+void doTarget(char* cmd) { command.scalar(&target_angle, cmd); }

+

+void setup() {

+

+ // use monitoring with serial

+ Serial.begin(115200);

+ // enable more verbose output for debugging

+ // comment out if not needed

+ SimpleFOCDebug::enable(&Serial);

+

+ // initialise magnetic sensor hardware

+ sensor.init();

+ // link the motor to the sensor

+ motor.linkSensor(&sensor);

+

+ // driver config

+ // power supply voltage [V]

+ driver.voltage_power_supply = 12;

+ driver.init();

+ // link the motor and the driver

+ motor.linkDriver(&driver);

+

+ // choose FOC modulation (optional)

+ motor.foc_modulation = FOCModulationType::SpaceVectorPWM;

+

+ // set motion control loop to be used

+ motor.controller = MotionControlType::angle;

+

+ // contoller configuration

+ // default parameters in defaults.h

+

+ // velocity PI controller parameters

+ motor.PID_velocity.P = 0.2f;

+ motor.PID_velocity.I = 20;

+ // maximal voltage to be set to the motor

+ motor.voltage_limit = 6;

+

+ // velocity low pass filtering time constant

+ // the lower the less filtered

+ motor.LPF_velocity.Tf = 0.01f;

+

+ // angle P controller

+ motor.P_angle.P = 20;

+ // maximal velocity of the position control

+ motor.velocity_limit = 40;

+

+ // comment out if not needed

+ motor.useMonitoring(Serial);

+

+

+ // initialize motor

+ motor.init();

+ // align sensor and start FOC

+ motor.initFOC();

+

+ // add target command T

+ command.add('T', doTarget, "target angle");

+

+ Serial.println(F("Motor ready."));

+ Serial.println(F("Set the target angle using serial terminal:"));

+ _delay(1000);

+}

+

+void loop() {

+

+ // main FOC algorithm function

+ // the faster you run this function the better

+ // Arduino UNO loop ~1kHz

+ // Bluepill loop ~10kHz

+ motor.loopFOC();

+

+ // Motion control function

+ // velocity, position or voltage (defined in motor.controller)

+ // this function can be run at much lower frequency than loopFOC() function

+ // You can also use motor.move() and set the motor.target in the code

+ motor.move(target_angle);

+

+

+ // function intended to be used with serial plotter to monitor motor variables

+ // significantly slowing the execution down!!!!

+ // motor.monitor();

+

+ // user communication

+ command.run();

+}

\ No newline at end of file

diff --git a/embedded/CANFDMigrate/.pio/libdeps/seeed_xiao_esp32s3/Simple FOC/examples/hardware_specific_examples/HMBGC_example/position_control/position_control.ino b/embedded/CANFDMigrate/.pio/libdeps/seeed_xiao_esp32s3/Simple FOC/examples/hardware_specific_examples/HMBGC_example/position_control/position_control.ino

new file mode 100644

index 0000000..d910765

--- /dev/null

+++ b/embedded/CANFDMigrate/.pio/libdeps/seeed_xiao_esp32s3/Simple FOC/examples/hardware_specific_examples/HMBGC_example/position_control/position_control.ino

@@ -0,0 +1,127 @@

+/**

+ *

+ * HMBGC position motion control example with encoder

+ *

+ * - Motor is connected the MOT1 connector (MOT1 9,10,11; MOT2 3,5,6)

+ * - Encoder is connected to A0 and A1

+ *

+ * This board doesn't have any interrupt pins so we need to run all the encoder channels with the software interrupt library

+ * - For this example we use: PciManager library : https://github.com/prampec/arduino-pcimanager

+ *

+ * See docs.simplefoc.com for more info.

+ *

+ */

+#include

+// software interrupt library

+#include

+#include

+

+

+// BLDC motor & driver instance

+BLDCMotor motor = BLDCMotor(11);

+BLDCDriver3PWM driver = BLDCDriver3PWM(9, 10, 11);

+

+// encoder instance

+Encoder encoder = Encoder(A0, A1, 2048);

+

+// Interrupt routine intialisation

+// channel A and B callbacks

+void doA(){encoder.handleA();}

+void doB(){encoder.handleB();}

+

+// encoder interrupt init

+PciListenerImp listenerA(encoder.pinA, doA);

+PciListenerImp listenerB(encoder.pinB, doB);

+

+

+// angle set point variable

+float target_angle = 0;

+// instantiate the commander

+Commander command = Commander(Serial);

+void doTarget(char* cmd) { command.scalar(&target_angle, cmd); }

+

+void setup() {

+

+ // use monitoring with serial

+ Serial.begin(115200);

+

+ // initialise encoder hardware

+ encoder.init();

+ // interrupt initialization

+ PciManager.registerListener(&listenerA);

+ PciManager.registerListener(&listenerB);

+ // link the motor to the sensor

+ motor.linkSensor(&encoder);

+

+ // driver config

+ // power supply voltage [V]

+ driver.voltage_power_supply = 12;

+ driver.init();

+ // link the motor and the driver

+ motor.linkDriver(&driver);

+

+ // aligning voltage [V]

+ motor.voltage_sensor_align = 3;

+ // index search velocity [rad/s]

+ motor.velocity_index_search = 3;

+

+ // set motion control loop to be used

+ motor.controller = MotionControlType::angle;

+

+ // contoller configuration

+ // default parameters in defaults.h

+

+ // velocity PI controller parameters

+ motor.PID_velocity.P = 0.2f;

+ motor.PID_velocity.I = 20;

+ // default voltage_power_supply

+ motor.voltage_limit = 6;

+ // jerk control using voltage voltage ramp

+ // default value is 300 volts per sec ~ 0.3V per millisecond

+ motor.PID_velocity.output_ramp = 1000;

+

+ // velocity low pass filtering time constant

+ motor.LPF_velocity.Tf = 0.01f;

+

+ // angle P controller

+ motor.P_angle.P = 20;

+ // maximal velocity of the position control

+ motor.velocity_limit = 4;

+

+ // comment out if not needed

+ motor.useMonitoring(Serial);

+

+ // initialize motor

+ motor.init();

+ // align encoder and start FOC

+ motor.initFOC();

+

+ // add target command T

+ command.add('T', doTarget, "target angle");

+

+ Serial.println(F("Motor ready."));

+ Serial.println(F("Set the target angle using serial terminal:"));

+ _delay(1000);

+}

+

+

+void loop() {

+ // main FOC algorithm function

+ // the faster you run this function the better

+ // Arduino UNO loop ~1kHz

+ // Bluepill loop ~10kHz

+ motor.loopFOC();

+

+ // Motion control function

+ // velocity, position or voltage (defined in motor.controller)

+ // this function can be run at much lower frequency than loopFOC() function

+ // You can also use motor.move() and set the motor.target in the code

+ motor.move(target_angle);

+

+ // function intended to be used with serial plotter to monitor motor variables

+ // significantly slowing the execution down!!!!

+ // motor.monitor();

+

+ // user communication

+ command.run();

+}

\ No newline at end of file

diff --git a/embedded/CANFDMigrate/.pio/libdeps/seeed_xiao_esp32s3/Simple FOC/examples/hardware_specific_examples/HMBGC_example/voltage_control/voltage_control.ino b/embedded/CANFDMigrate/.pio/libdeps/seeed_xiao_esp32s3/Simple FOC/examples/hardware_specific_examples/HMBGC_example/voltage_control/voltage_control.ino

new file mode 100644

index 0000000..9c9655f

--- /dev/null

+++ b/embedded/CANFDMigrate/.pio/libdeps/seeed_xiao_esp32s3/Simple FOC/examples/hardware_specific_examples/HMBGC_example/voltage_control/voltage_control.ino

@@ -0,0 +1,110 @@

+/**

+ *

+ * HMBGC torque control example using voltage control loop.

+ *

+ * - Motor is connected the MOT1 connector (MOT1 9,10,11; MOT2 3,5,6)

+ * - Encoder is connected to A0 and A1

+ *

+ * Most of the low-end BLDC driver boards doesn't have current measurement therefore SimpleFOC offers

+ * you a way to control motor torque by setting the voltage to the motor instead hte current.

+ *

+ * This makes the BLDC motor effectively a DC motor, and you can use it in a same way. position motion control example with encoder

+ *

+ * NOTE:

+ * > HMBGC doesn't have any interrupt pins so we need to run all the encoder channels with the software interrupt library

+ * > - For this example we use: PciManager library : https://github.com/prampec/arduino-pcimanager

+ *

+ * See docs.simplefoc.com for more info.

+ *

+ */

+#include

+// software interrupt library

+#include

+#include

+

+

+// BLDC motor & driver instance

+BLDCMotor motor = BLDCMotor(11);

+BLDCDriver3PWM driver = BLDCDriver3PWM(9, 10, 11);

+

+// encoder instance

+Encoder encoder = Encoder(A0, A1, 8192);

+

+// Interrupt routine intialisation

+// channel A and B callbacks

+void doA(){encoder.handleA();}

+void doB(){encoder.handleB();}

+

+// encoder interrupt init

+PciListenerImp listenerA(encoder.pinA, doA);

+PciListenerImp listenerB(encoder.pinB, doB);

+

+

+// voltage set point variable

+float target_voltage = 2;

+// instantiate the commander

+Commander command = Commander(Serial);

+void doTarget(char* cmd) { command.scalar(&target_voltage, cmd); }

+

+void setup() {

+

+ // initialize encoder sensor hardware

+ encoder.init();

+ // interrupt initialization

+ PciManager.registerListener(&listenerA);

+ PciManager.registerListener(&listenerB);

+ // link the motor to the sensor

+ motor.linkSensor(&encoder);

+

+ // driver config

+ // power supply voltage [V]

+ driver.voltage_power_supply = 12;

+ driver.init();

+ // link the motor and the driver

+ motor.linkDriver(&driver);

+

+ // choose FOC modulation (optional)

+ motor.foc_modulation = FOCModulationType::SpaceVectorPWM;

+

+ // set motion control loop to be used

+ motor.controller = MotionControlType::torque;

+

+ // use monitoring with serial for motor init

+ // comment out if not needed

+ motor.useMonitoring(Serial);

+

+ // use monitoring with serial

+ Serial.begin(115200);

+ // comment out if not needed

+ motor.useMonitoring(Serial);

+

+ // initialize motor

+ motor.init();

+ // align sensor and start FOC

+ motor.initFOC();

+

+ // add target command T

+ command.add('T', doTarget, "target voltage");

+

+ Serial.println(F("Motor ready."));

+ Serial.println(F("Set the target voltage using serial terminal:"));

+ _delay(1000);

+}

+

+void loop() {

+

+ // main FOC algorithm function

+ // the faster you run this function the better

+ // Arduino UNO loop ~1kHz

+ // Bluepill loop ~10kHz

+ motor.loopFOC();

+

+ // Motion control function

+ // velocity, position or voltage (defined in motor.controller)

+ // this function can be run at much lower frequency than loopFOC() function

+ // You can also use motor.move() and set the motor.target in the code

+ motor.move(target_voltage);

+

+ // user communication

+ command.run();

+}

\ No newline at end of file

diff --git a/embedded/CANFDMigrate/.pio/libdeps/seeed_xiao_esp32s3/Simple FOC/examples/hardware_specific_examples/Odrive_examples/odrive_example_encoder/odrive_example_encoder.ino b/embedded/CANFDMigrate/.pio/libdeps/seeed_xiao_esp32s3/Simple FOC/examples/hardware_specific_examples/Odrive_examples/odrive_example_encoder/odrive_example_encoder.ino

new file mode 100644

index 0000000..504ab9c

--- /dev/null

+++ b/embedded/CANFDMigrate/.pio/libdeps/seeed_xiao_esp32s3/Simple FOC/examples/hardware_specific_examples/Odrive_examples/odrive_example_encoder/odrive_example_encoder.ino

@@ -0,0 +1,138 @@

+/*

+ Odrive robotics' hardware is one of the best BLDC motor foc supporting hardware out there.

+

+ This is an example code that can be directly uploaded to the Odrive using the SWD programmer.

+ This code uses an encoder with 500 cpr and a BLDC motor with 7 pole pairs connected to the M0 interface of the Odrive.

+

+ This is a short template code and the idea is that you are able to adapt to your needs not to be a complete solution. :D

+*/

+#include

+

+// Odrive M0 motor pinout

+#define M0_INH_A PA8

+#define M0_INH_B PA9

+#define M0_INH_C PA10

+#define M0_INL_A PB13

+#define M0_INL_B PB14

+#define M0_INL_C PB15

+// M0 currnets

+#define M0_IB PC0

+#define M0_IC PC1

+// Odrive M0 encoder pinout

+#define M0_ENC_A PB4

+#define M0_ENC_B PB5

+#define M0_ENC_Z PC9

+

+

+// Odrive M1 motor pinout

+#define M1_INH_A PC6

+#define M1_INH_B PC7

+#define M1_INH_C PC8

+#define M1_INL_A PA7

+#define M1_INL_B PB0

+#define M1_INL_C PB1

+// M0 currnets

+#define M1_IB PC2

+#define M1_IC PC3

+// Odrive M1 encoder pinout

+#define M1_ENC_A PB6

+#define M1_ENC_B PB7

+#define M1_ENC_Z PC15

+

+// M1 & M2 common enable pin

+#define EN_GATE PB12

+

+// SPI pinout

+#define SPI3_SCL PC10

+#define SPI3_MISO PC11

+#define SPI3_MOSO PC12

+

+// Motor instance

+BLDCMotor motor = BLDCMotor(7);

+BLDCDriver6PWM driver = BLDCDriver6PWM(M0_INH_A,M0_INL_A, M0_INH_B,M0_INL_B, M0_INH_C,M0_INL_C, EN_GATE);

+

+// instantiate the commander

+Commander command = Commander(Serial);

+void doMotor(char* cmd) { command.motor(&motor, cmd); }

+

+// low side current sensing define

+// 0.0005 Ohm resistor

+// gain of 10x

+// current sensing on B and C phases, phase A not connected

+LowsideCurrentSense current_sense = LowsideCurrentSense(0.0005f, 10.0f, _NC, M0_IB, M0_IC);

+

+Encoder encoder = Encoder(M0_ENC_A, M0_ENC_B, 500,M0_ENC_Z);

+// Interrupt routine intialisation

+// channel A and B callbacks

+void doA(){encoder.handleA();}

+void doB(){encoder.handleB();}

+void doI(){encoder.handleIndex();}

+

+void setup(){

+

+ // use monitoring with serial

+ Serial.begin(115200);

+ // enable more verbose output for debugging

+ // comment out if not needed

+ SimpleFOCDebug::enable(&Serial);

+

+ // pwm frequency to be used [Hz]

+ driver.pwm_frequency = 20000;

+ // power supply voltage [V]

+ driver.voltage_power_supply = 20;

+ // Max DC voltage allowed - default voltage_power_supply

+ driver.voltage_limit = 20;

+ // driver init

+ driver.init();

+ // link the motor and the driver

+ motor.linkDriver(&driver);

+

+ // initialize encoder sensor hardware

+ encoder.init();

+ encoder.enableInterrupts(doA, doB, doI);

+ // link the motor to the sensor

+ motor.linkSensor(&encoder);

+

+ // control loop type and torque mode

+ motor.torque_controller = TorqueControlType::voltage;

+ motor.controller = MotionControlType::torque;

+

+ // max voltage allowed for motion control

+ motor.voltage_limit = 8.0;

+ // alignment voltage limit

+ motor.voltage_sensor_align = 0.5;

+

+ // comment out if not needed

+ motor.useMonitoring(Serial);

+ motor.monitor_variables = _MON_CURR_Q | _MON_CURR_D;

+ motor.monitor_downsample = 1000;

+

+ // add target command T

+ command.add('M', doMotor, "motor M0");

+

+ // initialise motor

+ motor.init();

+

+ // link the driver

+ current_sense.linkDriver(&driver);

+ // init the current sense

+ current_sense.init();

+ current_sense.skip_align = true;

+ motor.linkCurrentSense(¤t_sense);

+

+ // init FOC

+ motor.initFOC();

+ delay(1000);

+}

+

+void loop(){

+

+ // foc loop

+ motor.loopFOC();

+ // motion control

+ motor.move();

+ // monitoring

+ motor.monitor();

+ // user communication

+ command.run();

+}

\ No newline at end of file

diff --git a/embedded/CANFDMigrate/.pio/libdeps/seeed_xiao_esp32s3/Simple FOC/examples/hardware_specific_examples/Odrive_examples/odrive_example_spi/odrive_example_spi.ino b/embedded/CANFDMigrate/.pio/libdeps/seeed_xiao_esp32s3/Simple FOC/examples/hardware_specific_examples/Odrive_examples/odrive_example_spi/odrive_example_spi.ino

new file mode 100644

index 0000000..7abcde5

--- /dev/null

+++ b/embedded/CANFDMigrate/.pio/libdeps/seeed_xiao_esp32s3/Simple FOC/examples/hardware_specific_examples/Odrive_examples/odrive_example_spi/odrive_example_spi.ino

@@ -0,0 +1,136 @@

+/*

+ Odrive robotics' hardware is one of the best BLDC motor foc supporting hardware out there.

+

+ This is an example code that can be directly uploaded to the Odrive using the SWD programmer.

+ This code uses an magnetic spi sensor AS5047 and a BLDC motor with 11 pole pairs connected to the M0 interface of the Odrive.

+

+ This is a short template code and the idea is that you are able to adapt to your needs not to be a complete solution. :D

+*/

+#include

+

+// Odrive M0 motor pinout

+#define M0_INH_A PA8

+#define M0_INH_B PA9

+#define M0_INH_C PA10

+#define M0_INL_A PB13

+#define M0_INL_B PB14

+#define M0_INL_C PB15

+// M0 currnets

+#define M0_IB PC0

+#define M0_IC PC1

+// Odrive M0 encoder pinout

+#define M0_ENC_A PB4

+#define M0_ENC_B PB5

+#define M0_ENC_Z PC9

+

+

+// Odrive M1 motor pinout

+#define M1_INH_A PC6

+#define M1_INH_B PC7

+#define M1_INH_C PC8

+#define M1_INL_A PA7

+#define M1_INL_B PB0

+#define M1_INL_C PB1

+// M0 currnets

+#define M1_IB PC2

+#define M1_IC PC3

+// Odrive M1 encoder pinout

+#define M1_ENC_A PB6

+#define M1_ENC_B PB7

+#define M1_ENC_Z PC15

+

+// M1 & M2 common enable pin

+#define EN_GATE PB12

+

+// SPI pinout

+#define SPI3_SCL PC10

+#define SPI3_MISO PC11

+#define SPI3_MOSO PC12

+

+// Motor instance

+BLDCMotor motor = BLDCMotor(11);

+BLDCDriver6PWM driver = BLDCDriver6PWM(M0_INH_A,M0_INL_A, M0_INH_B,M0_INL_B, M0_INH_C,M0_INL_C, EN_GATE);

+

+// instantiate the commander

+Commander command = Commander(Serial);

+void doMotor(char* cmd) { command.motor(&motor, cmd); }

+

+// low side current sensing define

+// 0.0005 Ohm resistor

+// gain of 10x

+// current sensing on B and C phases, phase A not connected

+LowsideCurrentSense current_sense = LowsideCurrentSense(0.0005f, 10.0f, _NC, M0_IB, M0_IC);

+

+// MagneticSensorSPI(int cs, float _cpr, int _angle_register)

+// config - SPI config

+// cs - SPI chip select pin

+MagneticSensorSPI sensor = MagneticSensorSPI(AS5147_SPI, M0_ENC_A);

+SPIClass SPI_3(SPI3_MOSO, SPI3_MISO, SPI3_SCL);

+

+void setup(){

+

+ // use monitoring with serial

+ Serial.begin(115200);

+ // enable more verbose output for debugging

+ // comment out if not needed

+ SimpleFOCDebug::enable(&Serial);

+

+ // pwm frequency to be used [Hz]

+ driver.pwm_frequency = 20000;

+ // power supply voltage [V]

+ driver.voltage_power_supply = 20;

+ // Max DC voltage allowed - default voltage_power_supply

+ driver.voltage_limit = 20;

+ // driver init

+ driver.init();

+ // link the motor and the driver

+ motor.linkDriver(&driver);

+

+ // initialise magnetic sensor hardware

+ sensor.init(&SPI_3);

+ // link the motor to the sensor

+ motor.linkSensor(&sensor);

+

+ // control loop type and torque mode

+ motor.torque_controller = TorqueControlType::voltage;

+ motor.controller = MotionControlType::torque;

+

+ // max voltage allowed for motion control

+ motor.voltage_limit = 8.0;

+ // alignment voltage limit

+ motor.voltage_sensor_align = 0.5;

+

+ // comment out if not needed

+ motor.useMonitoring(Serial);

+ motor.monitor_variables = _MON_CURR_Q | _MON_CURR_D;

+ motor.monitor_downsample = 1000;

+

+ // add target command T

+ command.add('M', doMotor, "motor M0");

+

+ // initialise motor

+ motor.init();

+

+ // link the driver

+ current_sense.linkDriver(&driver);

+ // init the current sense

+ current_sense.init();

+ current_sense.skip_align = true;

+ motor.linkCurrentSense(¤t_sense);

+

+ // init FOC

+ motor.initFOC();

+ delay(1000);

+}

+

+void loop(){

+

+ // foc loop

+ motor.loopFOC();

+ // motion control

+ motor.move();

+ // monitoring

+ motor.monitor();

+ // user communication

+ command.run();

+}

\ No newline at end of file

diff --git a/embedded/CANFDMigrate/.pio/libdeps/seeed_xiao_esp32s3/Simple FOC/examples/hardware_specific_examples/SAMD_examples/README.md b/embedded/CANFDMigrate/.pio/libdeps/seeed_xiao_esp32s3/Simple FOC/examples/hardware_specific_examples/SAMD_examples/README.md

new file mode 100644

index 0000000..d1a5258

--- /dev/null

+++ b/embedded/CANFDMigrate/.pio/libdeps/seeed_xiao_esp32s3/Simple FOC/examples/hardware_specific_examples/SAMD_examples/README.md

@@ -0,0 +1,62 @@

+

+# SAMD Support

+

+SimpleFOC supports many SAMD21 MCUs, really any SAMD21 supported by Arduino core should work.

+

+## Pin assignments

+

+The SAMD chips have some very powerful PWM features, but do not have flexible pin assignments.

+

+You should be able to use *most* (but not all!), pin combinations for attaching your motor's PWM pins. Please ignore the board descriptions and pinout diagrammes regarding PWM-pins on SAMD boards. They are pretty much all incorrect to varying degrees of awfulness.

+

+On SAMD we use TCC and TC timer peripherals (built into the SAMD chip) to control the PWM. Depending on the chip there are various timer units, whose PWM outputs are attached to various different pins, and it is all very complicated. Luckily SimpleFOC sets it all up automatically *if* there is a compatible configuration for those pins.

+

+Not all timers are created equal. The TCC timers are pretty awesome for PWM motor control, while the TC timers are just ok for the job. So to get best performance, you want to use just TCC timer pins if you can.

+

+By enabling

+

+```

+ #define SIMPLEFOC_SAMD_DEBUG

+```

+

+in drivers/hardware_specific/samd_mcu.cpp

+you will see a table of pin assignments printed on the serial console, as well as the timers SimpleFOC was able to find and configure on the pins you specified. You can use this to optimize your choice of pins if you want.

+

+You can configure up to 12 pins for PWM motor control, i.e. 6x 2-PWM motors, 4x 3-PWM motors, 3x 4-PWM motors or 2x 6-PWM motors.

+

+## PWM control modes

+

+All modes (3-PWM, 6-PWM, Stepper 2-PWM and Stepper 4-PWM) are supported.

+

+For 2-, 3- amd 4- PWM, any valid pin-combinations can be used. If you stick to TCC timers rather than using TC timers, then you'll get getter PWM waveforms. If you use pins which are all on the same TCC unit, you'll get the best result, with the PWM signals all perfectly aligned as well.

+

+For 6-PWM, the situation is much more complicated:

+TC timers cannot be used for 6-PWM, only TCC timers.

+

+For Hardware Dead-Time insertion, you must use H and L pins for one phase from the same TCC unit, and on the same channel, but using complementary WOs (Waveform Outputs, i.e. PWM output pins). Check the table to find pins on the same channel (like TCC0-0) but complementary WOs (like TCC0-0[0] and TCC0-0[4] or TCC1-0[0] and TCC1-0[2]).

+

+For Software Dead-Time insertion, you must use the same TCC and different channels for the H and L pins of the same phase.

+

+Note: in all of the above note that you *cannot* set the timers or WOs used - they are fixed, and determined by the pins you selected. SimpleFOC will find the best combination of timers given the pins, trying to use TCC timers before TC, and trying to keep things on the same timers as much as possible. If you configure multiple motors, it will take into account the pins already assigned to other motors.

+So it is matter of choosing the right pins, nothing else.

+

+Note also: Unfortunately you can't set the PWM frequency. It is currently fixed at 24KHz. This is a tradeoff between limiting PWM resolution vs

+increasing frequency, and also due to keeping the pin assignemts flexible, which would not be possible if we ran the timers at different rates.

+

+## Status

+

+Currently, SAMD21 is supported, and SAMD51 is unsupported. SAMD51 support is in progress.

+

+Boards tested:

+

+ * Arduino Nano 33 IoT

+ * Arduino MKR1000

+ * Arduino MKR1010 Wifi

+ * Seeduino XIAO

+ * Feather M0 Basic

+

+Environments tested:

+

+ * Arduino IDE

+ * Arduino Pro IDE

+ * Sloeber